操作系统——多处理器和多核架构

目录

在传统上,计算机被看作一个序列机器。大部分计算机程序语言都要求程序员将算法具体化为一系列指令序列。处理器按顺序,一次执行一条计算机指令的方式运行程序。按照操作的顺序(取指令,取操作数,执行操作,存储结果),一条一条地执行计算机指令。

从这种视角看计算机从来都是不完全正确的。在微操作层面,多控制信号是同时产生的。至少,指令流水线在重叠获取和执行操作的范围内已经存在了很长的时间。这两者都是并行执行功能的例子。

计算机技术的演进,并且随着计算机硬件价格的下降,计算机设计者们已获得得了越来越多的并行化机会,通常用于改善性能,在某些情况下,用于改善可靠性。主要包括对称多处理器(Symmetric multiprocessors,简记为SMPs),多核计算器和集群。

1. 对称多处理器计算机系统

1.1 定义

一台对称多处理机可以定义为具有下列特征的一台独立的计算机系统:

(1) 存在两个或两个以上处理能力相当的相类似的处理器。

(2) 这些处理器共享相同的主存和I/O设施,以及通过一条总线或者其它内部连接系统互连,使得每个处理器访问内存的时间接近一致。

(3) 所有的处理器通过使用相同的通道或者提供访问相同设备的其它不同通道共享访问I/O设备。

(4) 所有处理器可以完成相同的功能(正所谓“对称”之意)。

(5) 系统通过集成的操作系统控制,集成操作系统提供处理器与它们的程序在作业、任务、文件、以及数据元素层面的交互。

(1)到(4) 显而易见。第 5 点说明了与松散耦合的多处理系统(例如集群)的对比之一。后者,交互的物理单元通常是一条消息或者一个完整的文件。在一台对称多处理机中,单个元素可以构成交互层面,并且可以构成进程之间更高程度的协作。

1.2 优点

一个对称多处理架构相较于单处理器架构而言,有许多潜在的优点,包括:

(1) 性能: 假如计算机完成的工作可以人分解成按并行方式执行,则多处理器比同一类型的单处理器能产生更好的性能。

(2) 可用性: 在对称多处理系统中,由于所有处理器都可以单独完成所有的功能,因此,单个处理器执行失败并不会使整个机器挂起。相反,系统会继续以降低的性能继续执行任务。

(3) 增量扩展: 用户可以通过增加额外处理器的方式来增强系统的性能。

(4) 伸缩性: 产品供应商可以按照系统配置的处理器数量提供具有不同价格和性能特征的广泛范围的产品。

注意,这些优点是潜在的,而不是必备的。操作系统必须提供相应的工作和功能来挖掘对称多处理系统的并行性。

一个对称多处理系统的具有吸引力的特征在于多处理器对于用户是透明的。操作系统负责基于单个处理器的任务切换调度,以及多个处理器之间同步的任务调度。

1.3 架构

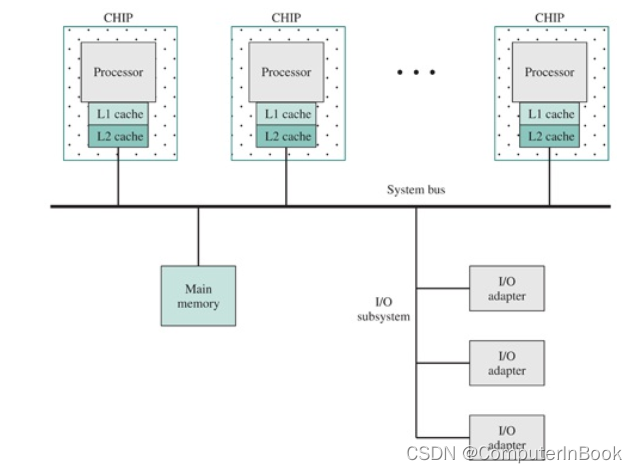

下图1-1展示了对称多处理器的通用架构。存在多个处理器,每个处理器包括有其独立的控制单元,算术逻辑单元,以及寄存器(对于程序员而言,要明白系统不只一套寄存器,而是每个处理器一套寄存器)。典型的是,每个处理器有两级专用的缓存,分别记为L1和L2。正如图所示,每个处理器与其专用的缓存都安装在单独的芯片上。每个处理器通过相同形式的互联机制共享访问主存;一条共享总线是通用设施。处理器可以通过内存(留在共享地址空间上的消息和状态信息)互相通信。内存通常是有组织的,因此可以同时访问多个单独的内存块。

-----------------------图1.19 对称多处理器系统架构---------------------------------

在现代计算机中,处理器通常至少有一个自己私有的一级缓存。这种缓存用法引入了一些新的考量。因为每个逻辑缓存包括一个主存一部分的映像。因为一个字在一个缓存中被更改,它可能想得到的结果是使另一个缓存中的一个字无效。为防止这种情况发生,必须提醒其他处理器已发生更新。这个问题被称为缓存一致性问题,通常在硬件而不是操作系统中解决这个问题。

2. 多核处理器计算机系统

2.1 定义

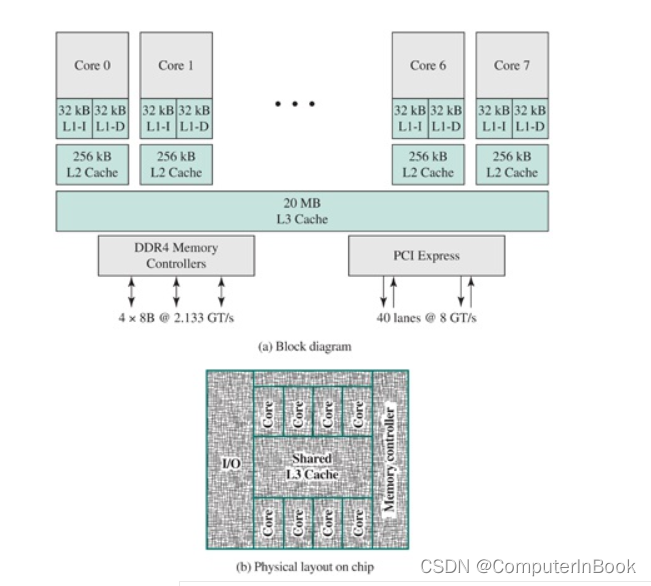

多核计算机(multicore),也称为单芯片多处理器(chip multiprocessor),是在一块单独的硅片(称为芯片)上集成两个或多个处理器(称为核)。典型情况是,每一个核由单个处理器的所有组件构成,例如,包括寄存器,算术逻辑单元,流水线硬件,和控制单元,再加一级指令和数据缓存(L1)。除了多核,当代多核芯片包括二级缓存(L2)以及,部分包括三级缓存(L3)(这一点对于程序员也很重要,多核处理器每个内核包括一套自己单独的寄存器)。

开发多核计算机的动机可以概括如下。几十年来,微处理器系统的性能一直在稳步增长,通常呈指数级增长。这部分是由于硬件趋势,例如时钟频率的增加以及由于微型计算机组件的日益小型化而使高速缓存更靠近处理器的能力。通过增加处理器设计的复杂性来利用指令执行和内存访问中的并行性,性能也得到了提高。简而言之,设计人员在通过更复杂的处理器实现更高性能的能力方面遇到了实际限制。设计人员发现,提高性能以利用硬件进步的最佳方法是将多个处理器和大量高速缓存放在单个芯片上。对这一趋势的基本原理的详细讨论超出了我们目前的范围。

2.2 多核示例

多核系统的一个示例是Intel Core i7-5960X,它包括6个X86处理器,每一个处理器有一个专用的二级缓存(L2),以及一个共享的三级缓存(L3)。Intel用于使缓存更加有效的一种机制叫预取(prefetching),其中硬件检查内存访问模式并尝试用可能很快会请求的数据推测性地填充缓存。下图1-2显示了5960X在其芯片上的物理布局。

-------------------图1-2 Intel Core i7-5960X 架构图--------------------------------------

Core i7-5960X支持两种形式的外部通讯。DDR4内存控制器将DDR(双倍数据速率)主内存的内存控制器带入芯片。该接口支持4个8字节宽(64位)的通道,总的总线宽度为256 位,总数据速率高达 64 GB/s。 有了芯片上的内存控制器,前端总线就被淘汰了。 PCI Express 是一种外围总线,可在连接的处理器芯片之间实现高速通信。PCI Express链路以 8 GT/s(每秒传输)的速度运行。每次传输40位,总计 40 GB/s。

参考资料:

<<Operating Systems: Internals and Design Principles >> 9th William Stallings