数字后端物理设计输入文件介绍(.v .sdc .lib/.db .lef .tlef/.tf rc corner .view)

Physical Design input files

Inputs for Physical Design | Physical Design input files

Remark:Team VLSI

In Physical Design mainly Six inputs are present

- Logical libraries --> format is .lib —>given by Vendors

- physical libraries -->format is .lef —>given by vendors

- Technology file -->format is .tf —>given by fabrication peoples

- TLU+ file -->format is .TLUP–>given by fabrication people

- Netlist —>format is .v -->given by Synthesis People

- Synthesis Design Constraints -->format is .SDC -->given by Synthesis People

- .upf —>> for multivoltage design given by Design team

Outputs —>> .def , .v and .enc.dat (Innovus ) or .nlib (ICC2)

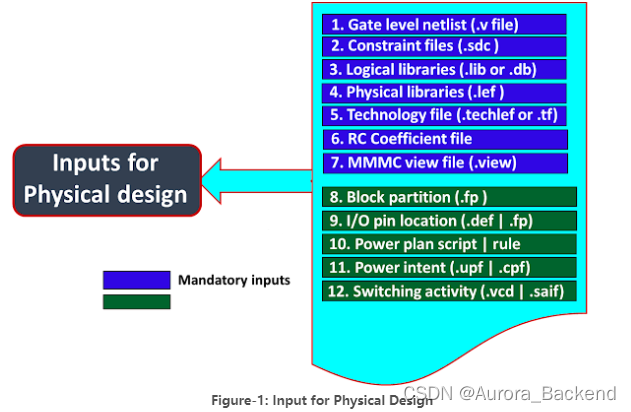

物理设计所需的输入可大致分为两类。有些输入在所有情况下都是强制mandatory必须要有的,但有些输入是为了特定的目的而可选的。

图1显示了物理设计所需的输入列表,并对必须的输入和可选输入mandatory and optional inputs进行了分类。

mandatory inputs(必须要有的输入文件)

需要下述文件集来启动所有物理设计,Cadence 工具和 Synopsys 工具的一些文件格式不同。

Design-related files(设计库)

In the set input files, the first set is design-related files which contain Gate level netlist file and design constraint files. These files come from the synthesis team. Let’s briefly see the content of these files.

1.Gate level netlist(.v)

This is the synthesized netlist. The synthesis team performs synthesis on RTL code with the standard cell libraries and constraints and converts the RTL code into the gate-level netlist based on available standard cells. This file contains all the instances of design and their connection.

综合团队使用标准单元库和约束对 RTL 代码进行综合,并根据可用的标准单元将 RTL 代码转换为门级网表。该文件包含此文件包含所有设计实例及其连接情况。

2.Constraint file(.sdc)(Synopsys Design Constraints)

约束文件通常被称为 SDC 文件,因为它是文件的扩展名。它基本上包含:

- Units (Time, Capacitance, Resistance, Voltage, Current, Power) / 单位(时间,电容,电阻,电压,电流,功率)

- System interface (Driving cell, load) / 系统接口(驱动单元,负载)

- Design rule constraints (max fanout, max transition)

- Timing constraints (Clock definitions, clock latency, clock uncertainty, input/output delay)

- Timing exceptions (Multi-cycle and false paths)

Now some inputs are required which are related to standard cell libraries. These files are provided by the standard cell library vendor and these files are as follows.

现在需要一些与标准单元库相关的输入。这些文件由标准单元库供应商提供,这些文件如下所示:

3.Logical libraries(.lib or .db)(逻辑库/时序功耗库)

逻辑库也称为时序库或功能库或功耗库timing library or functional library or power library,因为它包含了单元的功能、时间和电源信息 functionality, time and power information of cells。此文件基本上包含standard cells或macro的以下信息。

- Timing details of the standard cells / macros ( delay, transitions)

- Setup and hold time of standard cells / macros

- Functionality details of standard cells /macros

- Area of standard cells / macros

- Pin directions and capacitance

- Leakage power of standard cells / macros

The logical libraries could be either in liberty format .lib file for Cadence tool or in the form of .db file for Synopsys tool.对于不同的 PVT Corner有不同的逻辑库,Liberty 文件是通过标准单元库角色塑造创建的,所以这个文件是由标准单元库供应商提供的。

(.lib)文件和(.db)文件两者所记录的内容是一样的,都是记录单元时序、功能、功耗的文件,只不过lib是文本文件,cadence家工具读取的文件格式,我们可以直接打开这个文件来阅读里面的内容。而db是synopsys家读取的文件格式,synopsys为了加快文件读取的速度,会把lib转化为db格式,db是一个二进制不可读的文件,文件加载速度会快于lib。

4. Physical libraries(.lef)(物理库)

The physical library contains the abstract view of the layout for standard cells and macros. LEF file basically contains:

- Size of the cell (Height and width)

- Symmetry of cell (对称性)

- Pins name, direction, use, shape, layer

- Pins location

Physical libraries are in Library Exchange Format (.lef) for the Cadence tools or .CELL and .FRAM form for Synopsys tool. This file is provided by the standard cell library vendor. (这个文件是由标准单元库供应商提供的)

5.Technology file(.tlef/.tf)(技术文件)

The technology library is the most critical input to the physical design tool. The technology library contains detailed information about all the metal layers, vias and their design rules. This file is in ASCII format and basically contains the following information:

技术文件是对物理设计工具最关键的输入。技术库包含有关所有金属层、通孔及其设计规则的详细信息。该文件采用 ASCII 格式,基本上包含以下信息:

- Manufacturing grid

- Layers name (poly | contact | metal1 |via2 )

- Types and the direction of the metal

- Pitch(pitch一般是最小间距和最小线宽之和。space是同一层metal之间的间距。)

- Width

- Spacing

- Resistance (per square unit)

The technology file used by the Cadence tool is .tlef format and .tf format by Synopsys tool.

6.RC coefficient(系数) file

TLU file is a short form of “Table Look-Up” used for RC estimation and extraction or we use QRC file or cap table for the same.

7.MMMC view file(.view)

Multi-Mode Multi-Corner file is used to generate different analysis views based on different delay corners and constraints modes. Delay corners are defined on library sets and RC corners. There are various library set files库设置文件 based on voltage and temperature values (like ss, ff, typical).

optional inputs(特定目的可选输入文件)

There are some optional files that might be required especially for block-level PnR implementation. These files are as below.

8.Block partition

For block-level PnR, we need a defined core area for the block or block partitions which defines the size and shape of the block. Block shape could be a simple rectangular or a complex rectilinear shape.

9.Pin def

For block-level PnR, pin locations have been decided by the Full chip owner and for block-level, we have to use the predecided pin location in order to match the pin locations with other blocks. Generally, it is given in form of a def file. In case of any pin placement issue at the block level, the block owner can inform the person who is placing the pin and if required block owner can also edit the pin placement.

10.Power plan script

For block-level PnR, the power plan should be as per the full chip. The power plan has been decided on full chip and in block level, the Power plan should be used as per full chip. A power plan could be given a set of rules or a power plan script (.tcl file).

11.Power intent (UPF | CPF file)

The power intent file describes which power rails should be routed to individual blocks and when the block should be powered on or shut down. Unified Power Format (.upf) (统一电源格式)and Common Power Format (.cpf) (通用电源格式)are two different formats of power intent files.CPF format is used by the Cadence tool and UPF format by the other tools. We must need this file if the block is having a multi-voltage domain.

12.Switching activity files (VCD | SAIF)

SAIF or VCD file is used basically for the dynamic IR analysis in the Physical design.Dynamic IR analysis provides the Dynamic power drop inside the chip based on the switching activities. (根据开关活动提供芯片内部的动态功率降。)

各阶段所需文件

1. Place and Route stages:

1.1 Pre Placement Stage

- Gate level netlist

- SDC file

- Logical Library

- Physical Library

Optional inputs

- Block partition def

- Pin def

- Power plan script

- Welltap placement rule

- Macro placement guidelines

- MMMC Setup file

- EndCap, Decap cell list

- Spare Cell module definition and rule

Logical Library, Physical Library and SDC file will be required in each stage.

Netlist will get modified(修改) in each stage and an updated netlist will be used in the next stage.

1.2 Placement

- Preplace database

Optional Inputs

- Placement blockage script

- Path groups script

- Placement setting script

- Timing and Congestion Optimization scripts

- Clock tree constraints (In case of Early Clock Flow)

1.3 CTS

- Placement database

- Clock tree constraints

1.4 Route

- CTS database

1.5 Chip Finish

- Route database

- Filler cell list

2.Metal Fill

- OASIS/GDS of Chip finish stage

3.RC Extraction(Starrc)

- ICT File / Quantus Techfile (qrcTechFile)

- MMMC setup file

- LEF

- DEF

- Merged OASIS/GDS file

4.IR Analysis

4.1 Technology/Library Data

- LEF file (.lef)

- LIB file (.lib)

- Technology file (.tech)

- GDS file of standard cells (.gds)

- GDS Layer map file

- Device model file*

- SPICE Netlist of Standard cells*

4.2 Design Data

- DEF file

- Netlist file

- SPEF file

- STA File* (Timing Window, slew, instance frequency, clock domain info)

- VCD file*

- PLOC file*

*Files required only for dynamic analysis

4.3 Types of IR Analysis:

-

I. Static IR Analysis

-

II. Dynamic IR Analysis

-

III. EM Analysis

5.Static Timing Analysis(Prime Time)

- Design Netlist

- SDC

- LIB

- SPEF

- MMMC view definition file

Optional inputs:

- Instance-based IR drop file

- SI library

- Base/Incr Delay annotation file

6.Physical Verification(Calibre)

6.1 DRC

- Merged GDS file

- DRC RuleDeck file

6.2 Layout Vs Schematic Check (LVS)

- PD Netlist

- Merged GDS file

6.3 Antenna

- Merged GDS file

- DRC RuleDeck file

6.4 Logic Equivelence Check (LEC)

- Golden Netlist

- PD Netlist

- LEC Constraints (if any)